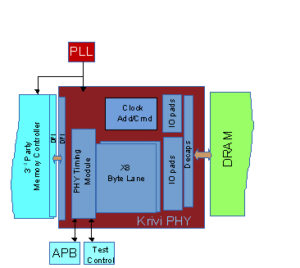

Memory Interface (DDR) PHY

Krivi offers DFI compatible DDR PHYs to best fit in your SoC with reasonable cost and time. Our DDR PHYs are available in hardened and semi-soft formats to suit your requirements. Our advanced silicon proven PHY solution takes care of all the complex DDR timings using fine step analog DLL and jitter tolerant training algorithms. Along with partner companies, we provide complete DDR solution including Memory Controller, DDR VIP and package SI/PI sign-off.

We have experienced Digital, Analog, IO pad, CAD and Hardening teams working next to each other. It helps to optimize and provide best-in-class DDR PHY with least Power and Area.

Salient features of Krivi DDR PHY:

- Supports all current DDR PHY standards: DDR4/3/2, LPDDR3/2. LPDDR4 to be available soon.

- Synthesizable RTL along with superior analog DLL and propriety hardening flow enables custom configurations and easy hardening

- Achieve 3.2Gbps speed (simulation) in 28nm process node, 2.13Gbps achieved in 4-layer wire-bond silicon

- Comprehensive Training algorithms:

- Up to 4 chip select of independent training

- Recovers every static skew of entire DRAM READ and WRITE paths

- Captures full working EYE using deep 2UI READ/WRITE DQS centering & ½ UI per-bit DQ de-skewing

- Dynamic squelch training to track voltage and temperature variation

- VREF, CA and proprietary trainings to optimize performance

- Comprehensive low power features including auto IO shut-down and in-design hierarchical custom clock gating

- On-the-fly data width selection with in-rush current protection

- Easy SoC integration by using physically grouped DFI interface, simplified clocking and interface timing and PHY independent mode training

- Layered BIST for quick bring-up using PHY, IO or DRAM level full-speed loop-backs

- At-speed and stuck-at DFT

- Zero bring-up time

- Extensive programmability and debug register set

We have consistently achieved first time working IP thanks to rigorous verification environment that includes uncertainty enabled VIP, mixed mode simulation for Analog blocks and co SI/PI simulation of critical path from PHY PLL to DRAM ball.